# EE 435

# Lecture 4

# Spring 2021

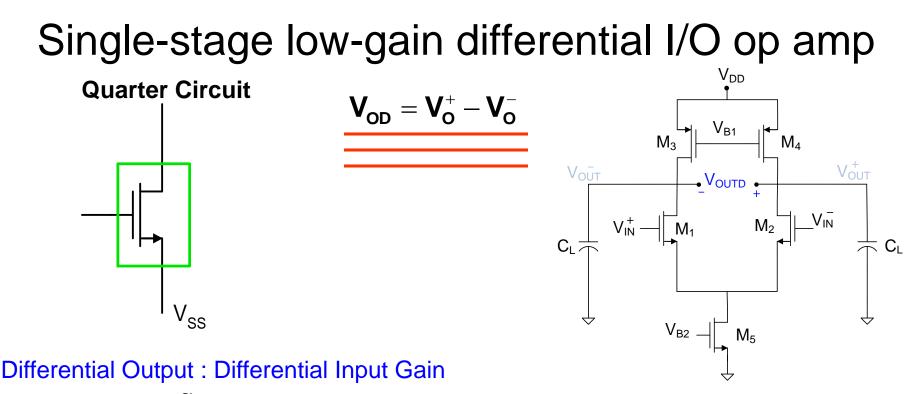

#### Fully Differential Single-Stage Amplifier Design

- General Differential Analysis

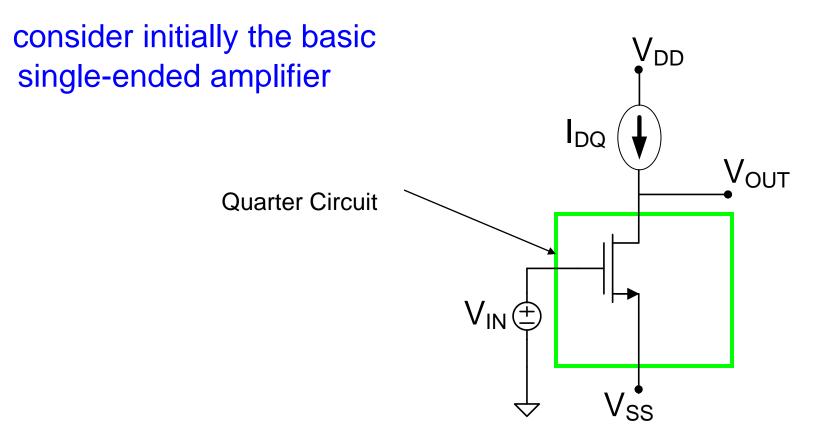

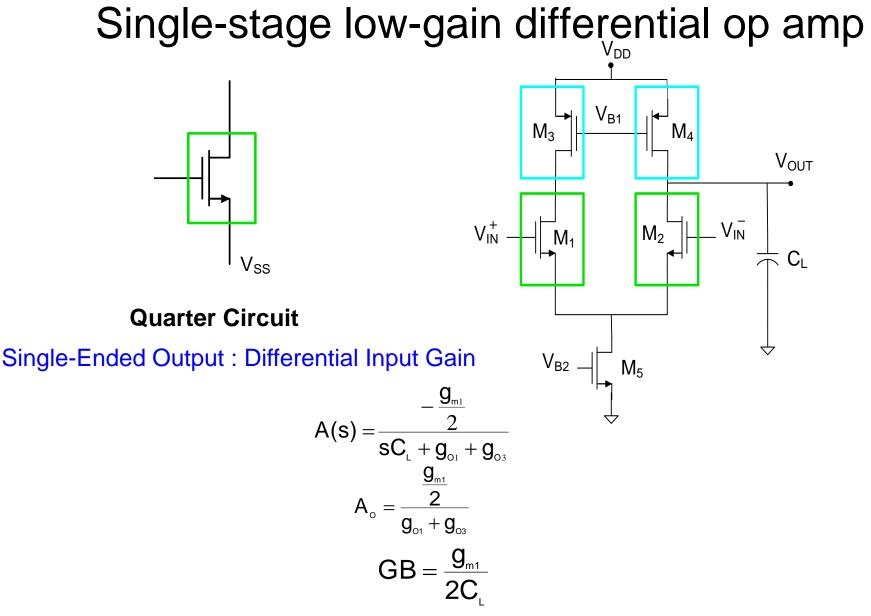

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- → Common-mode and differential-mode analysis

- → Common Mode Gain

- →• Overall Transfer Characteristics

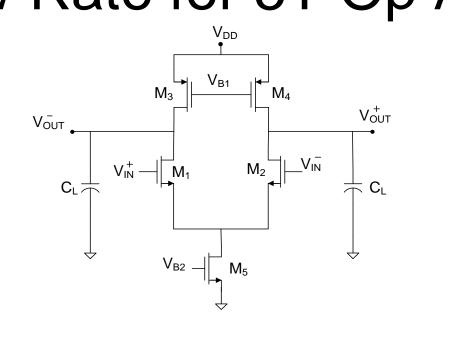

Design of 5T Op Amp Slew Rate

# Where we are at: Basic Op Amp Design

- Fundamental Amplifier Design Issues

- Single-Stage Low Gain Op Amps

- Single-Stage High Gain Op Amps

- Two-Stage Op Amp

- Other Basic Gain Enhancement Approaches

# Where we are at: Single-Stage Low-Gain Op Amps

Single-ended input

(Symbol does not distinguish between different amplifier types)

## Review from last lecture: Differential Input Low Gain Op Amps

Will Next Show That :

• Differential input op amps can be readily obtained from single-ended op amps

Performance characteristics of differential op amps can be directly determined from those of the single-ended counterparts

#### **Review from last lecture: Counterpart Networks**

Definition: The counterpart network of a network is obtained by replacing all n-channel devices with p-channel devices, replacing all p-channel devices with n-channel devices, replacing  $V_{SS}$  biases with  $V_{DD}$  biases, and replacing all  $V_{DD}$  biases with  $V_{SS}$  biases.

#### Review from last lecture: Counterpart Networks

Theorem: The parametric expressions for all small-signal characteristics, such as voltage gain, output impedance, and transconductance of a network and its counterpart network are the same.

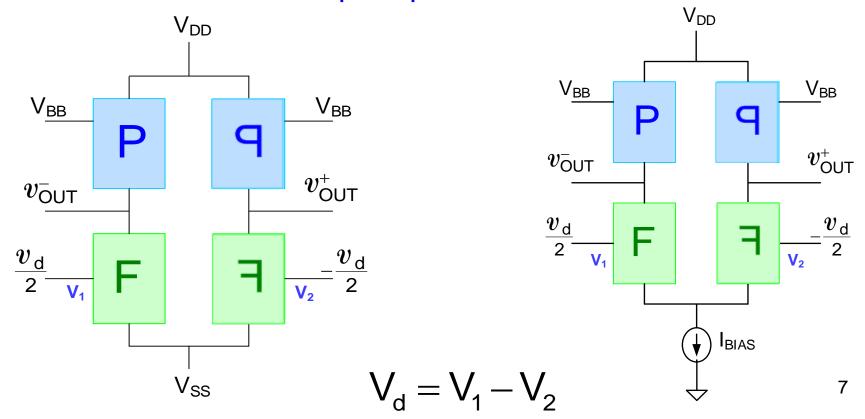

## Synthesis of fully-differential op amps from symmetric networks and counterpart networks

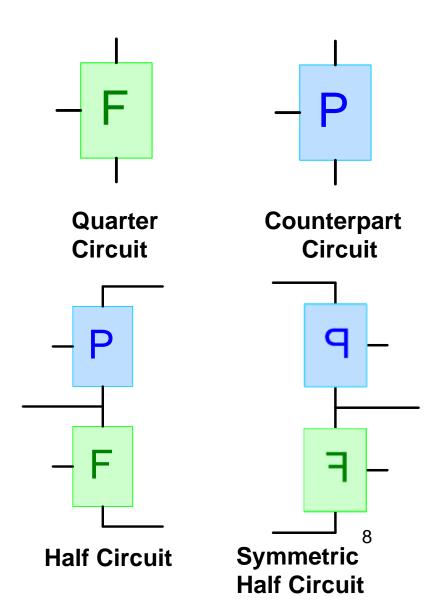

Theorem: If F is any network with a single input and P is its counterpart network, then the following circuits are fully differential circuits --- "op amps".

eview from

Synthesis of fully-differential op amps from symmetric networks and counterpart networks

Terminology

## Review from last lecture: Applications of Quarter-Circuit Concept to Op Amp Design

- Have synthesized fully differential op amp from quarter circuit !

- Have obtained analysis of fully differential op amp directly from quarter circuit !

10

- Still need to determine what happens if input is not differential !

- Have almost obtained op amp characteristics by inspection from quarter circuit !!

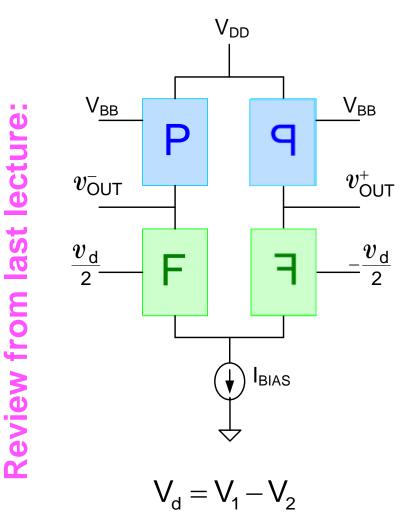

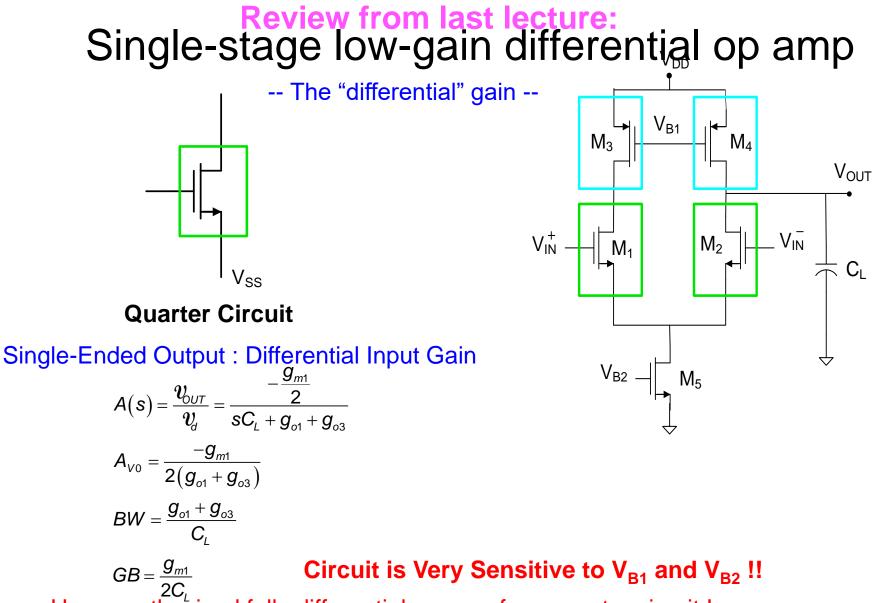

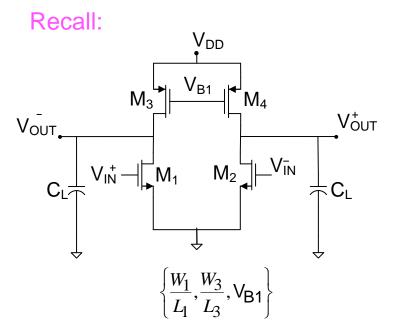

#### Review from last lecture:

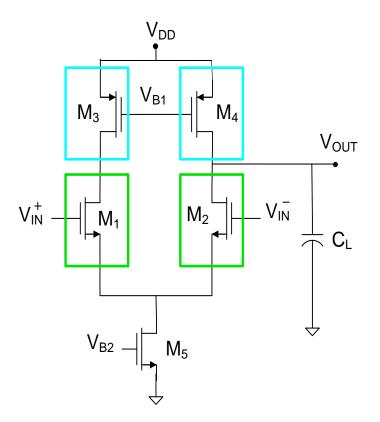

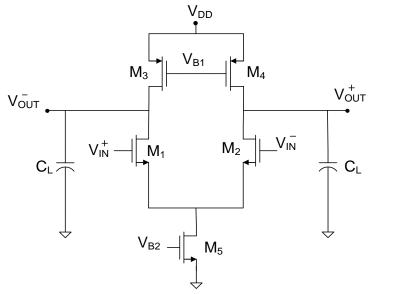

### Single-stage low-gain differential op amp

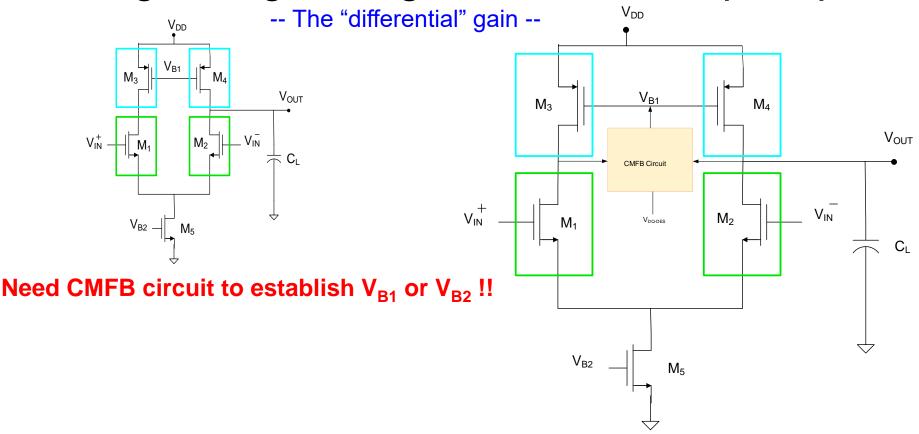

- CMFB circuit determines average value of the drain voltages

- Compares the average to the desired quiescent drain voltages

- Established a feedback signal  $V_{B1}$  to set the right Q-point

- Shown for V<sub>B1</sub> but could alternately be applied to V<sub>B2</sub>

#### Details about CMFB circuits will be discussed later

#### • Fully Differential Single-Stage Amplifier D

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

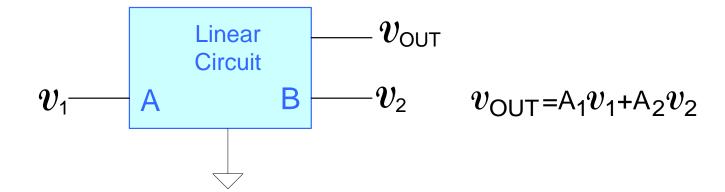

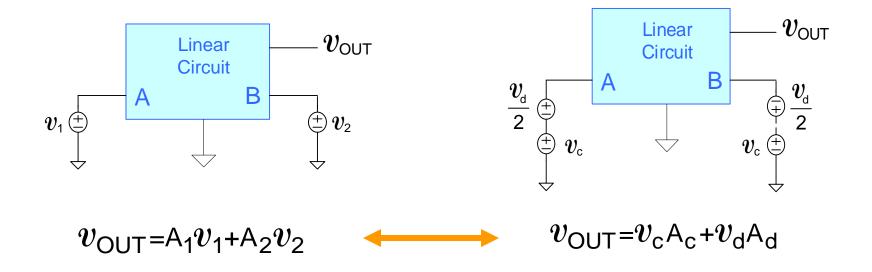

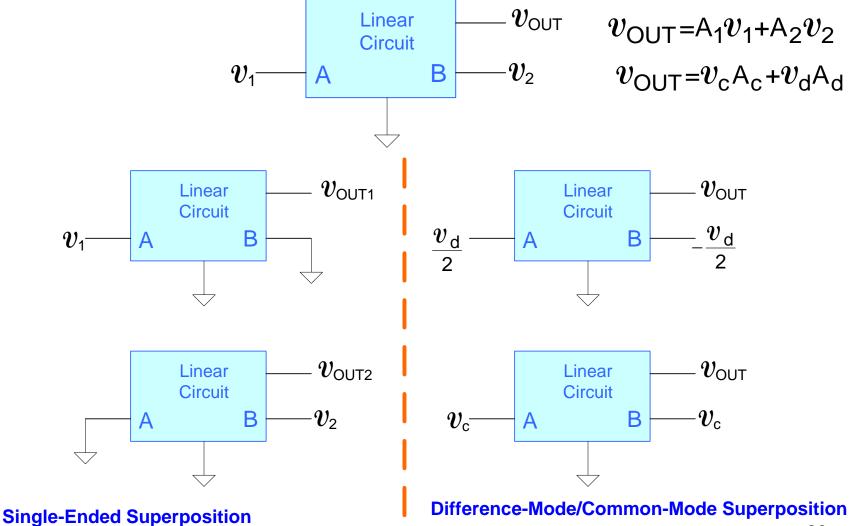

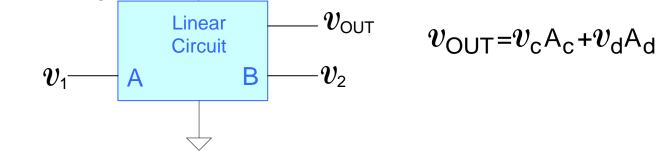

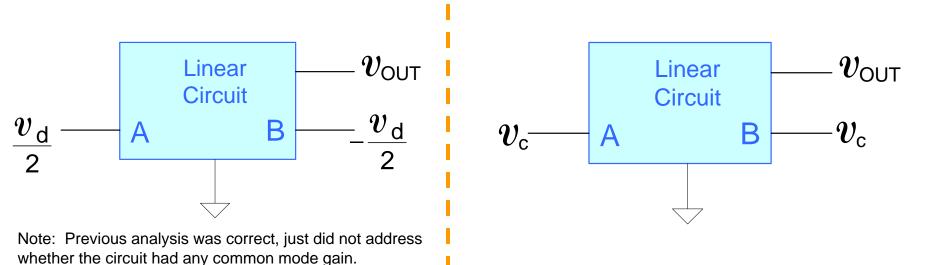

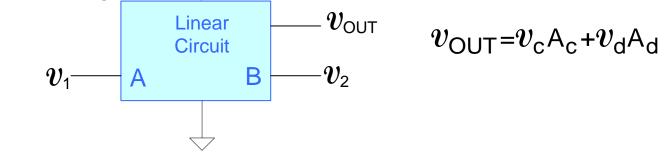

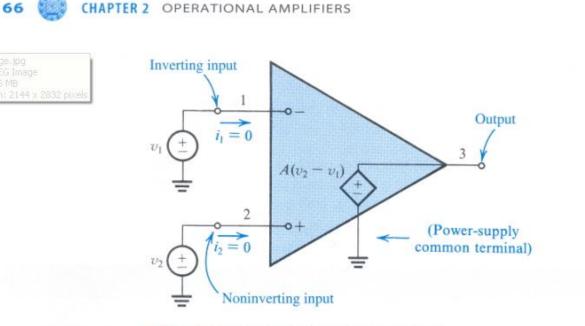

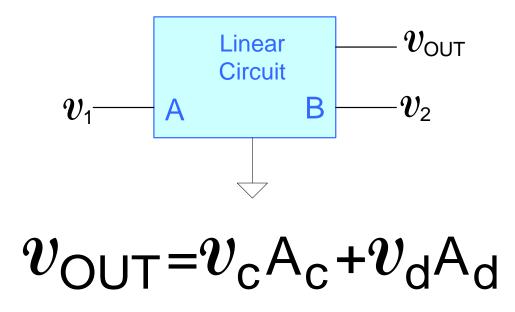

Consider <u>an</u> output voltage for any linear circuit with two inputs (i.e. need not be symmetric)

By superposition

$$v_{\text{OUT}} = A_1 v_1 + A_2 v_2$$

where  $A_1$  and  $A_2$  are the gains (transfer functions) from inputs 1 and 2 to the output respectively

Define the common-mode and difference-mode inputs by

$$v_{c} = \frac{v_{1} + v_{2}}{2}$$

$$v_{d} = v_{1} - v_{2}$$

These two equations can be solved for  $v_{1}$  and  $v_{2}$  to obtain

$$v_{1} = v_{c} + \frac{v_{d}}{2}$$

$$v_{2} = v_{c} - \frac{v_{d}}{2}$$

13

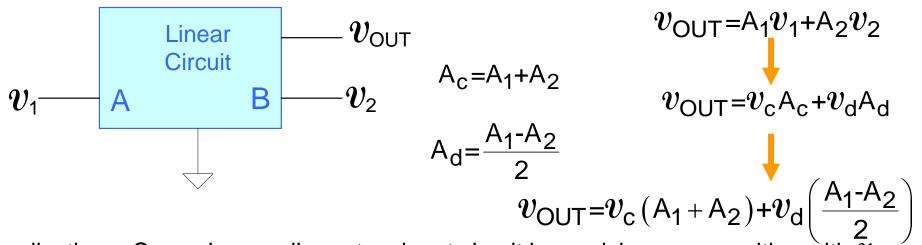

Consider an output voltage for any linear circuit with two inputs

Substituting into the expression for  $v_{\scriptscriptstyle ext{OUT}}$ , we obtain

$$v_{\text{OUT}} = A_1 \left( v_{\text{c}} + \frac{v_{\text{d}}}{2} \right) + A_2 \left( v_{\text{c}} - \frac{v_{\text{d}}}{2} \right)$$

Rearranging terms we obtain  $v_{OUT} = v_{O}$  (A

$$\operatorname{OUT} = \mathcal{V}_{c} \left( A_{1} + A_{2} \right) + \mathcal{V}_{d} \left( \frac{A_{1} - A_{2}}{2} \right)$$

If we define  $A_{\rm c}$  and  $A_{\rm d}$  by

$$A_c = A_1 + A_2 \qquad A_d = \frac{A_1 - A_2}{2}$$

Can express  $v_{\scriptscriptstyle \mathsf{OUT}}$  as

$$v_{OUT} = v_c A_c + v_d A_d$$

14

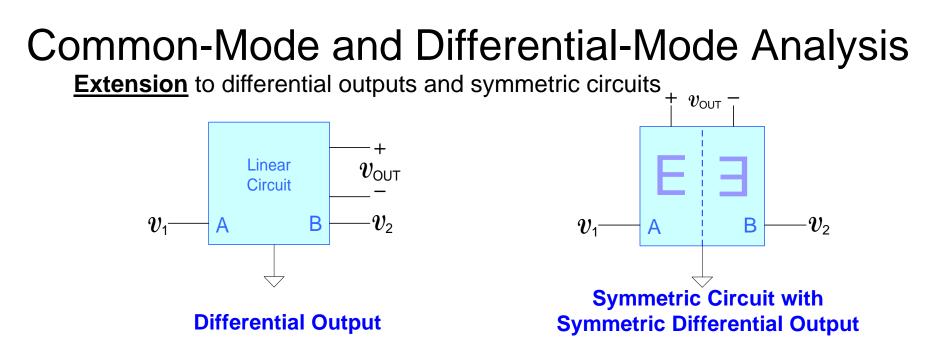

Depiction of singe-ended inputs and common/difference mode inputs

- Applicable to any linear circuit with two inputs and a single output

- Op amps often have symmetry and this symmetry further simplifies analysis

Consider <u>any</u> output voltage for any linear circuit with two inputs

Implication: Can solve any linear two-input circuit by applying superposition with  $v_1$  and  $v_2$  as inputs or with  $v_c$  and  $v_d$  as inputs. This can be summarized in the following theorem:

Theorem 1: The output for any linear network can be expressed equivalently as  $v_{OUT} = A_1 v_1 + A_2 v_2$  or as  $v_{OUT} = v_c A_c + v_d A_d$ Superposition can be applied to either  $v_1$  and  $v_2$  to obtain  $A_1$  and  $A_2$  or to  $v_c$  and  $v_d$  to obtain  $A_c$  and  $A_d$

Observation: In a circuit with  $A_2 = -A_1$ ,  $A_C = 0$  we obtain  $v_{OUT} = v_d A_d$

Analysis of op amps up to this point have assumed differential excitation

16

Observation: In a symmetric circuit with a symmetric differential output,  $A_c=0$  so can be shown that  $v_{OUT}=v_dA_d$  This is summarized in the theorem:

Theorem 2: The symmetric differential output voltage for any symmetric linear network excited at symmetric nodes can be expressed as

$$v_{\rm OUT} = A_{\rm d} v_{\rm d}$$

where A<sub>d</sub> is the differential voltage gain and the voltage  $v_{\rm d}$  =  $v_{\rm 1}$  -  $v_{\rm 2}$

#### Symmetric Circuit with Symmetric Differential Output

Theorem 2: The symmetric differential output voltage for any symmetric linear network excited at symmetric nodes can be expressed as

$$v_{\rm OUT} = A_{\rm d} v_{\rm d}$$

where A<sub>d</sub> is the differential voltage gain and the voltage  $v_{\rm d}$  =  $v_{\rm 1}$  -  $v_{\rm 2}$

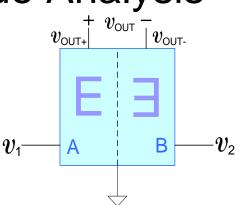

**Proof of Theorem 2 for Symmetric Circuit with Symmetric Differential Output:**

By superposition, the single-ended outputs can be expressed as

$v_{\text{OUT}}$  + = T<sub>0PA</sub> $v_1$  + T<sub>0PB</sub> $v_2$  $v_{\text{OUT}}$  = T<sub>0NA</sub> $v_1$  + T<sub>0NB</sub> $v_2$

where  $T_{0PA}$ ,  $T_{0PB}$ ,  $T_{0NA}$  and  $T_{0NB}$  are the transfer functions from the A and B inputs to the single-ended + and - outputs

taking the difference of these two equations we obtain

$$v_{\mathsf{OUT}}$$

=  $v_{\mathsf{OUT}+}$  -  $v_{\mathsf{OUT}-}$  =(T<sub>0PA</sub>-T<sub>0NA</sub>) $v_1$  +(T<sub>0PB</sub>-T<sub>0NB</sub>) $v_2$

by symmetry, we have

$T_{OPA} = T_{ONB}$  and  $T_{ONA} = T_{OPB}$

thus can express  $V_{\text{OUT}}$  as

$$\boldsymbol{v}_{\text{OUT}} = (\mathbf{T}_{\text{OPA}} - \mathbf{T}_{\text{ONA}})(\boldsymbol{v}_1 - \boldsymbol{v}_2)$$

or as

$$v_{\mathsf{OUT}}$$

=A $_{\mathsf{d}}v_{\mathsf{d}}$

where  $\rm A_{d}$  = T\_{OPA}\text{-}T\_{ONA} and where  $\upsilon_{\rm d}$  =  $\upsilon_{\rm 1}$  -  $\upsilon_{\rm 2}$

Consider any output voltage for any linear circuit with two inputs

Consider an output voltage for any linear circuit with two inputs

21

- Difference-Mode/Common-Mode Superposition is almost exclusively used for characterizing Amplifiers that are designed to have a large differential gain and a small common-mode gain

- Analysis to this point has been focused only on the circuit on the left

Will now get the total output of an amplifier circuit !

Consider an output voltage for any linear circuit with two inputs

Does Conventional Wisdom Address the Common Mode Gain Issue?

#### Does Conventional Wisdom Address the Common Mode Gain Issue?

Yes – Common-Mode Gain was Addressed

#### Does Conventional Wisdom Address the Common Mode Gain Issue?

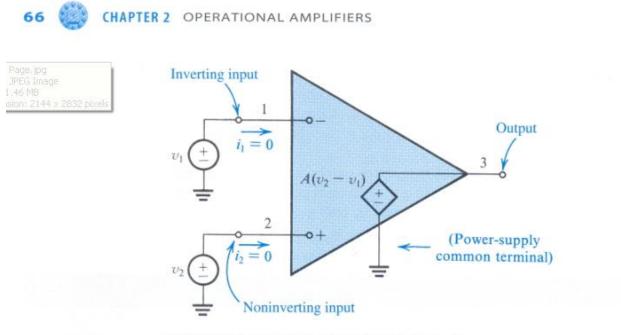

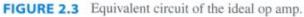

FIGURE 2.3 Equivalent circuit of the ideal op amp.

#### TABLE 2.1 Characteristics of the Ideal Op Amp

- 1. Infinite input impedance

- 2. Zero output impedance

- 3. Zero common-mode gain or, equivalently, infinite common-mode rejection

- 4. Infinite open-loop gain A

- 5. Infinite bandwidth

#### Yes – Common-Mode Gain was Addressed

## How is Common-Mode Gain Modeled?

If Op Amp is a Voltage Amplifier with infinite input impedance, zero output impedance, and one terminal of the output is grounded

#### • Fully Differential Single-Stage Amplifier D

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

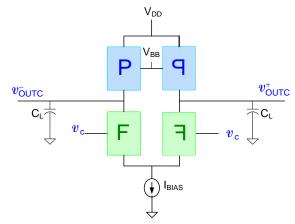

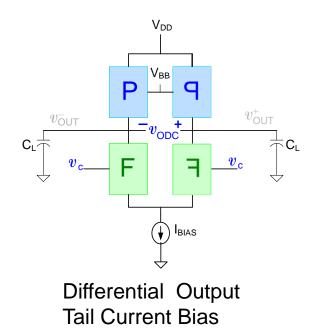

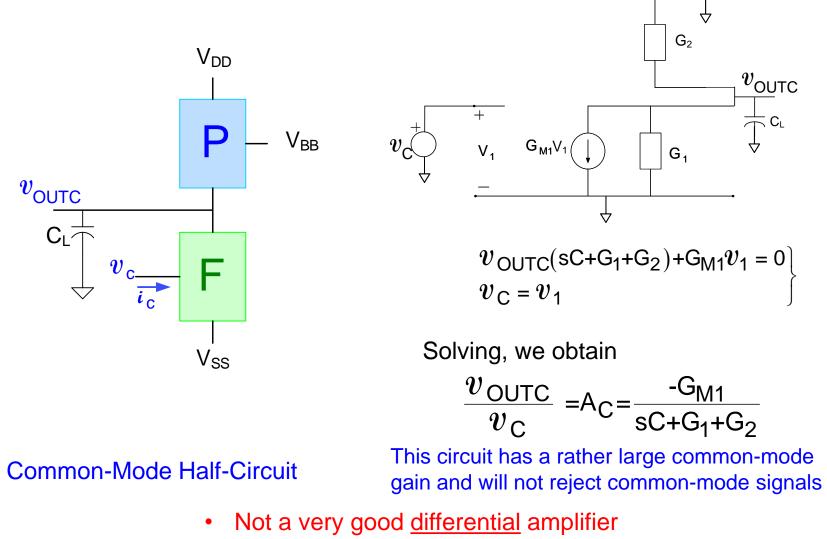

Single-Ended Outputs Tail-Current Bias

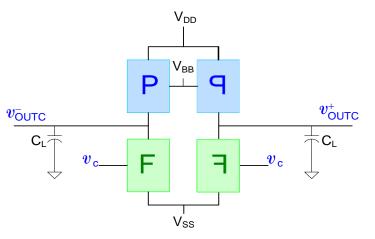

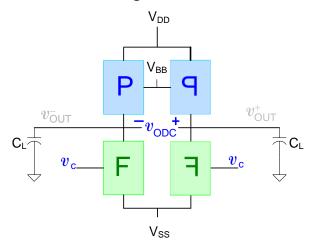

Single-Ended Outputs Tail-Voltage Bias

Differential Output 27 Tail Voltage Bias

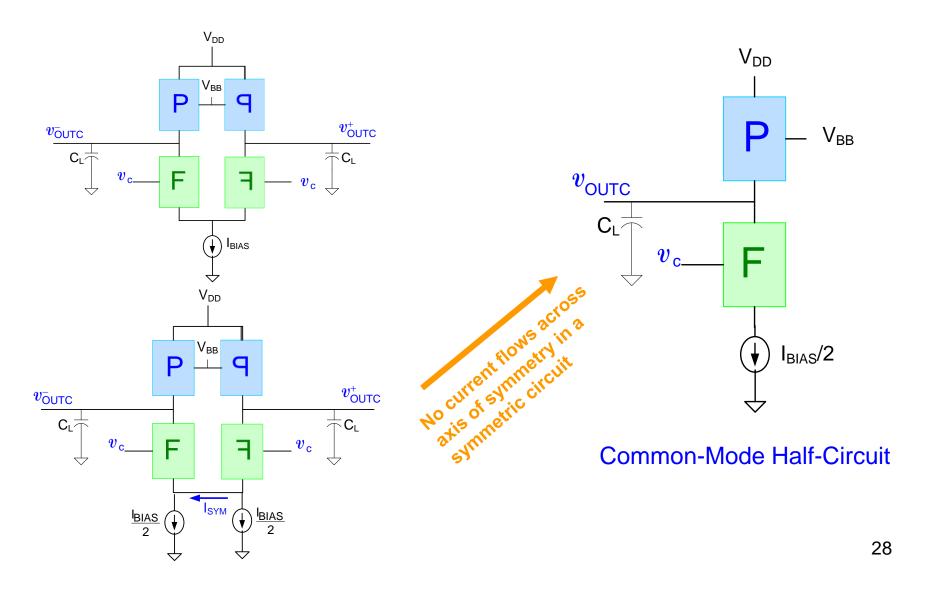

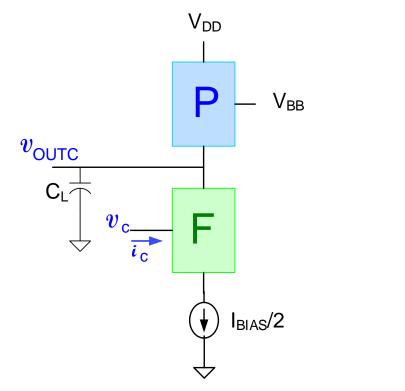

Consider tail-current bias amplifier

Consider tail-current bias amplifier with  $i_c=0$

$v_{OUTC}=0$  thus A<sub>C</sub>=0

#### Common-Mode Half-Circuit

(Note: Have assumed an ideal tail current source in this analysis A<sub>C</sub> will be small but may not vanish if tail current source is not ideal. Analysis with nonideal current source is simple)

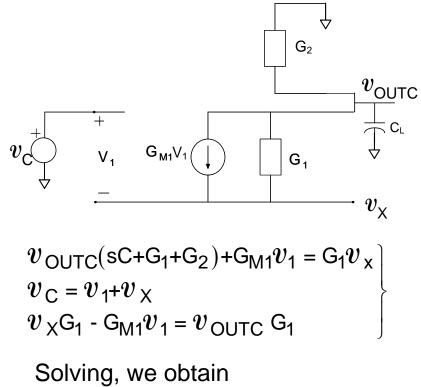

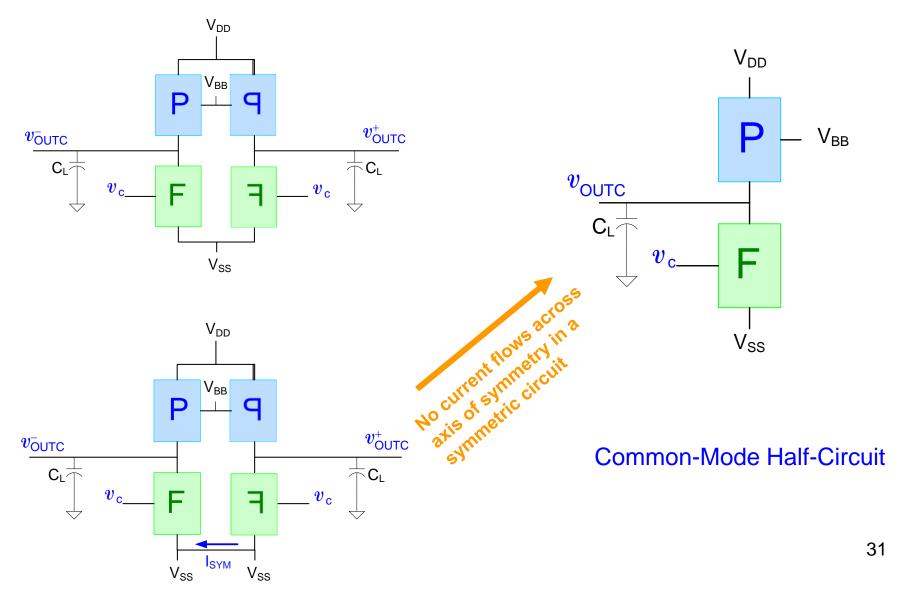

Consider tail-voltage bias amplifier with  $i_c=0$

Consider tail-voltage bias amplifier with  $i_c=0$

- But of no concern in applications where  $v_{\rm C}$ =0

32

#### • Fully Differential Single-Stage Amplifier D

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

## **Overall Small-Signal Analysis**

As stated earlier, with common-mode gain and difference-mode gains available

#### • Fully Differential Single-Stage Amplifier D

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

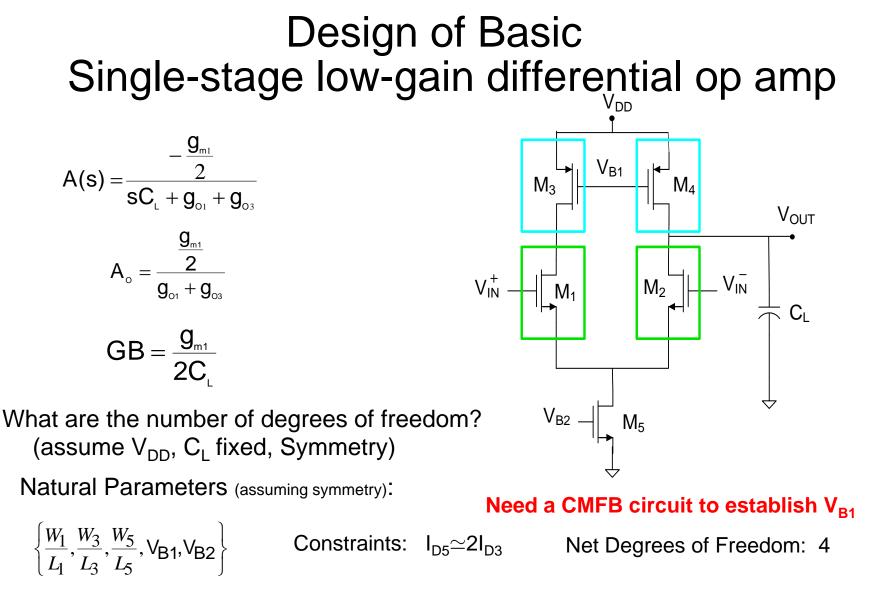

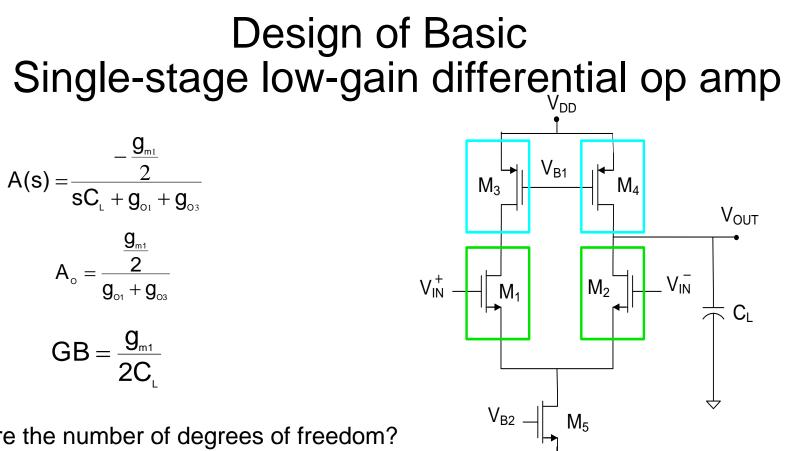

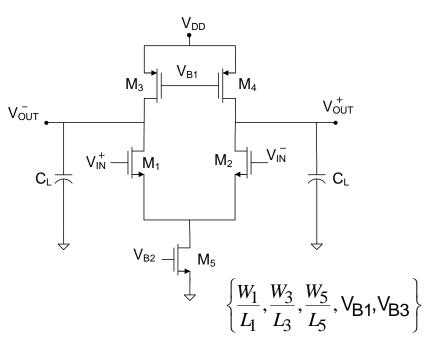

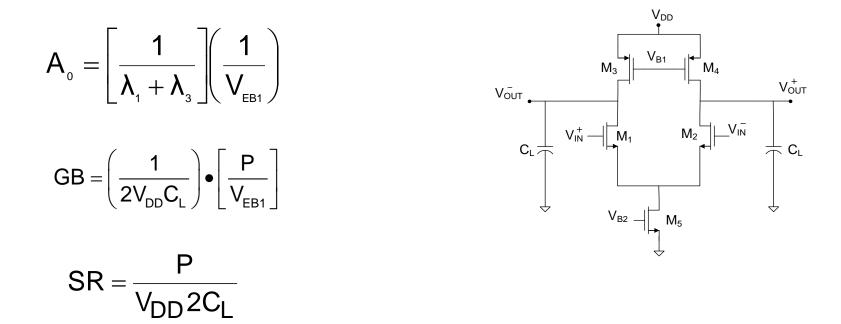

#### Design of 5T op amp

Need a CMFB circuit to establish V<sub>B1</sub>

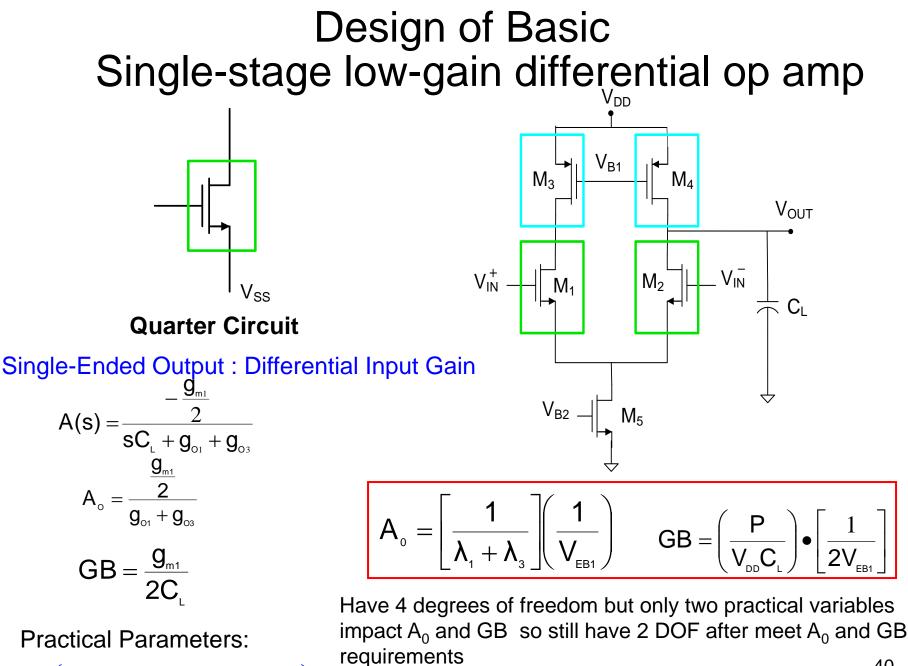

- Expressions for A<sub>0</sub> and GB were obtained from quarter-circuit

- Expressions for A<sub>0</sub> and GB in terms of natural parameters for quarter circuit were messy

- Can show that expressions for A<sub>0</sub> and GB in terms of natural parameters for 5T amplifier are also messy

#### Can a set of practical design parameters be identified?

Constraints:  $I_{D5} \simeq 2I_{D3}$

What are the number of degrees of freedom? (assume V<sub>DD</sub>, C<sub>L</sub> fixed, Symmetry)

Natural Parameters:

$\left\{\frac{W_1}{L_1}, \frac{W_3}{L_3}, \frac{W_5}{L_5}, \mathsf{V_{B1}}, \mathsf{V_{B2}}\right\}$

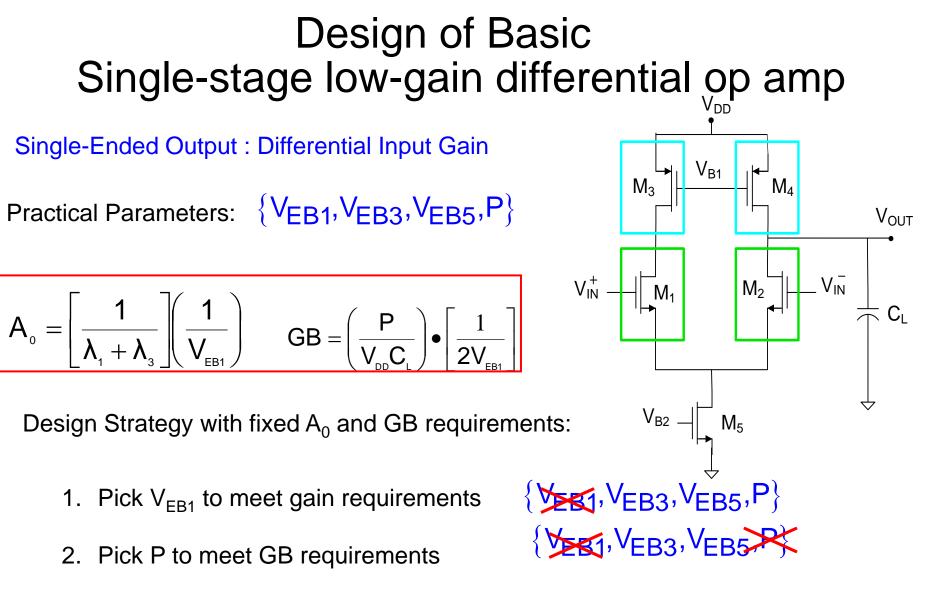

**Practical Parameters:**

$\left\{V_{\text{EB1}},V_{\text{EB3}},V_{\text{EB5}},P\right\}$

Will now express performance characteristics in terms of Practical Parameters 39

#### Need a CMFB circuit to establish $V_{B1}$

Net Degrees of Freedom: 4

$\{V_{EB1}, V_{EB3}, V_{EB5}, P\}$

#### Need a CMFB circuit to establish V<sub>B1</sub>

40

3. Pick  $V_{EB3}$  and  $V_{EB5}$  to achieve other desirable properties (i.e. explore the remaining part of the design space)

Note: Design strategy may change if  $A_0$  and GB are not firm requirements

$$A(s) = \frac{g_{m1}}{sC_{L} + g_{01} + g_{03}}$$

$$A_{0} = \frac{g_{m1}}{g_{01} + g_{03}}$$

$$GB = \frac{g_{m1}}{C_{L}}$$

$A_{_{0}} = \left[\frac{1}{\lambda_{_{1}} + \lambda_{_{3}}}\right] \left(\frac{2}{V_{_{EB1}}}\right) \quad GB = \left(\frac{P}{V_{_{DD}}C_{_{L}}}\right) \bullet \left[\frac{1}{V_{_{EB1}}}\right]$

Have 4 degrees of freedom but only two practical variables impact  $A_0$  and GB so still have 2 DOF after meet  $A_0$  and GB requirements that can be used for other purposes

#### Need a CMFB circuit to establish $V_{B1}$ or $V_{B2}^{42}$

#### A<sub>D</sub> expressions valid for both tail-current and tail-voltage op amp

#### So which one should be used?

- Common-mode input range large for tail current bias

- Improved rejection of common-mode signals for tail current bias

- Two extra design degree of freedom for tail current bias

- Improved output signal swing for tail voltage bias (will show later)

### • Fully Differential Single-Stage Amplifier D

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

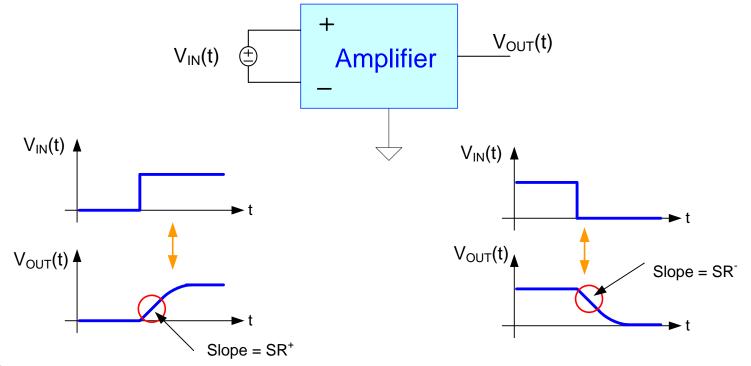

### **Slew Rate**

Definition: The slew rate of an amplifier is the maximum rate of change that can occur at the output node

- SR is a nonlinear large-signal characteristic

- Input is over-driven (some devices in amplifier usually leave normal operating region)

- Hard input overdrive depicted in this figure

- Magnitude of SR<sup>+</sup> and SR<sup>-</sup> usually same and called SR (else SR<sup>+</sup> and SR<sup>-</sup> must be given)

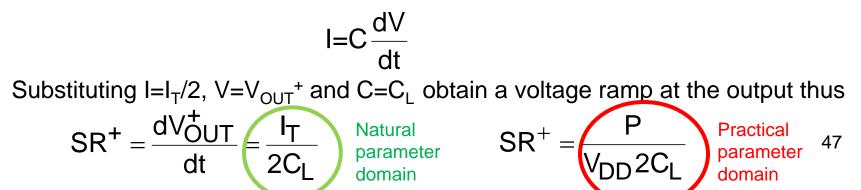

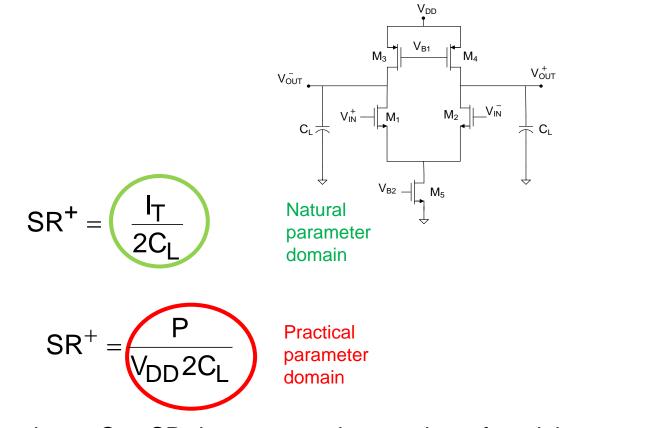

## Slew Rate for 5T Op Amp

With large step input on  $V_{IN}^+$ , all tail current  $(I_T)$  will go to  $M_1$  thus turning off  $M_2$  thus current through  $M_4$  which is  $\frac{1}{2}$  of  $I_T$  will go to load capacitor  $C_L$

The I-V characteristics of any capacitor is

### Slew Rate for 5T Op Amp

Question: Can SR<sup>+</sup> be expressed as product of model parameters and architecture dependent term?  $SR^{+} = \left[\frac{1}{2C_{I}}\right] [I_{T}] \qquad SR^{+} = \left[\frac{1}{V_{DD}2C_{I}}\right] [P]$

Question: Can SR<sup>+</sup> be expressed in small-signal parameter domain?

$$SR^{+} = \frac{g_{01}I_{T}}{\lambda 2C_{I}} = \left[\frac{I_{T}}{\lambda 2C_{I}}\right][g_{01}]$$

<sup>48</sup>

### **Slew Rate**

It can be similarly shown that putting a large negative step on the input steer all current to  $M_2$  thus the current to the capacitor  $C_L$  will be  $I_T$  minus the current from  $M_2$  which is still  $I_T/2$ . This will cause a negative ramp voltage on  $V_{OUT}^+$  of value

$$SR^{-} = \frac{dV_{OUT}^{+}}{dt} = -\frac{I_{T}}{2C_{L}} = -\frac{P}{V_{DD}2C_{L}}$$

Since the magnitude of SR<sup>+</sup> and SR<sup>-</sup> are the same, obtain a single SR for the amplifier of value

$$SR = \frac{P}{V_{DD} 2C_L}$$

<sup>49</sup>

### Interdependence of Parameters

50

Note: With this structure, the three key performance characteristics  $\{A_0, GB, SR\}$  can not be independently specified

e.g. If V<sub>EB1</sub> is picked to set A<sub>0</sub>, then  $\frac{P}{V_{DD}C_L}$  will determine both GB and SR Alternately, observe  $SR = \frac{GB}{A_0(\lambda_1 + \lambda_2)}$

### Stay Safe and Stay Healthy !

# End of Lecture 4